# **Application note**

# Ether**CAT** Slave Controller

- Section I Technology (Online at <u>http://www.beckhoff.com</u>)

- Section II Register description (Online at <u>http://www.beckhoff.com</u>)

# Section III – Hardware description (Online at http://www.beckhoff.com)

Application note – PHY selection guide Requirements to Ethernet PHYs used for EtherCAT and EtherCAT G Ethernet PHY Examples

Version 3.0 Date: 2024-03-08

#### DOCUMENT ORGANIZATION

The Beckhoff EtherCAT Slave Controller (ESC) documentation covers the following Beckhoff ESCs:

- ET1200 •

- ET1100

- EtherCAT IP Core for Altera<sup>®</sup> FPGAs

- EtherCAT IP Core for AMD<sup>®</sup>(Xilinx<sup>®</sup>) FPGAs

- ESC20

The documentation is organized in three sections. Section I and section II are common for all Beckhoff ESCs, Section III is specific for each ESC variant.

The latest documentation is available at the Beckhoff homepage (http://www.beckhoff.com).

#### Section I – Technology (All ESCs)

Section I deals with the basic EtherCAT technology. Starting with the EtherCAT protocol itself, the frame processing inside EtherCAT slaves is described. The features and interfaces of the physical layer with its two alternatives Ethernet and EBUS are explained afterwards. Finally, the details of the functional units of an ESC like FMMU, SyncManager, Distributed Clocks, Slave Information Interface, Interrupts, Watchdogs, and so on, are described.

Since Section I is common for all Beckhoff ESCs, it might describe features which are not available in a specific ESC. Refer to the feature details overview in Section III of a specific ESC to find out which features are available.

#### Section II – Register Description (All ESCs)

Section II contains detailed information about all ESC registers. This section is also common for all Beckhoff ESCs, thus registers, register bits, or features are described which might not be available in a specific ESC. Refer to the register overview and to the feature details overview in Section III of a specific ESC to find out which registers and features are available.

#### Section III – Hardware Description (Specific ESC)

Section III is ESC specific and contains detailed information about the ESC features, implemented registers. configuration, interfaces, pinout, usage, electrical and mechanical specification, and so on. Especially the Process Data Interfaces (PDI) supported by the ESC are part of this section.

#### **Additional Documentation**

Application notes and utilities can also be found at the Beckhoff homepage. Pinout configuration tools for ET1100/ET1200 are available. Additional information on EtherCAT IP Cores with latest updates regarding design flow compatibility, FPGA device support and known issues are also available.

#### Trademarks

Beckhoff®, TwinCAT®, TwinCAT/BSD®, TC/BSD®, EtherCAT®, EtherCAT G®, EtherCAT G10®, EtherCAT P®, Safety over EtherCAT®, TwinSAFE®, XFC®, XTS® and XPlanar® are registered trademarks of and licensed by Beckhoff Automation GmbH. Other designations used in this publication may be trademarks whose use by third parties for their own purposes could violate the rights of the owners.

#### Patent Pending

The EtherCAT Technology is covered, including but not limited to the following patent applications and patents: EP1590927, EP1789857, EP1456722, EP2137893, DE102015105702 with corresponding applications or registrations in various other countries

#### Disclaimer

The documentation has been prepared with care. The products described are, however, constantly under development. For that reason, the documentation is not in every case checked for consistency with performance data, standards or other characteristics. In the event that it contains technical or editorial errors, we retain the right to make alterations at any time and without warning. No claims for the modification of products that have already been supplied may be made on the basis of the data, diagrams and descriptions in this documentation

#### Copyright

© Beckhoff Automation GmbH & Co. KG 03/2024.

The reproduction, distribution and utilization of this document as well as the communication of its contents to others without express authorization are prohibited. Offenders will be held liable for the payment of damages. All rights reserved in the event of the grant of a patent, utility model or design.

| 1.1010 | r inst proliminary rolease                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.2    | <ul> <li>Ethernet PHY requirements revised (</li> <li>Added Microchip KSZ8001L</li> <li>Added Texas Instruments DP83848,</li> <li>Editorial changes</li> </ul>                                                                                                                                                                                                                                                                               |

| 1.3    | <ul> <li>Added restriction to enhanced link co<br/>outside of frames (IEEE802 optional</li> <li>Removed Texas Instruments DP838<br/>examination</li> </ul>                                                                                                                                                                                                                                                                                   |

| 1.4    | <ul> <li>Updated/clarified PHY requirements,</li> <li>Added Texas Instruments DP83848,</li> <li>Added PHYs which require Enhance</li> <li>Editorial changes</li> </ul>                                                                                                                                                                                                                                                                       |

| 1.5    | <ul> <li>PHY startup should not rely on MDC</li> <li>Added Microchip KSZ8041NL/TL Re<br/>EtherCAT with Enhanced Link Detec</li> <li>ESD tolerance and baseline wander</li> <li>Editorial changes</li> </ul>                                                                                                                                                                                                                                  |

| 1.6    | <ul><li>Completely revised and enhanced co</li><li>Editorial changes</li></ul>                                                                                                                                                                                                                                                                                                                                                               |

| 1.7    | <ul> <li>Added restrictions for ET1100-0002/<br/>Enhanced Link Detection: PHY addre</li> <li>PHY address offset for Teridian PHY</li> </ul>                                                                                                                                                                                                                                                                                                  |

| 1.8    | <ul> <li>Added Microchip KSZ8051 PHYs</li> <li>Link loss reaction time of Broadcom</li> <li>Clarified suitability of some Microchip<br/>ET1200</li> <li>Changed footnote: Microchip PIC10 i<br/>management address conversion du<br/>adding an extra MDC cycle)</li> </ul>                                                                                                                                                                   |

| 2.0    | <ul> <li>Microchip KSZ8051: update to rev. A</li> <li>Microchip KSZ8721: LED1 speed be</li> <li>Texas Instruments DP83848/DP8384</li> <li>Renesas µPD60610, µPD60611, µPI</li> <li>Microchip LAN8700 added</li> <li>STMicroelectronics STE802RT1A/B</li> <li>Texas Instruments DP83620/DP836</li> <li>Added chapter about EtherCAT over</li> <li>Added chapter about Gigabit Ethernet</li> <li>Enhanced recommendations for Ether</li> </ul> |

•

•

•

•

٠

•

2.1

2.2

Added required PHY signals table

RX ER is required for EtherCAT

Editorial changes

Version

1.1pre

Comment

First preliminary release

DOCUMENT HISTORY

| omment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| st preliminary release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Ethernet PHY requirements revised (e.g., link loss reaction time)<br>Added Microchip KSZ8001L                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Added Texas Instruments DP83848, DP83849, and DP83640<br>Editorial changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Added restriction to enhanced link configuration: RX_ER has to be asserted outside of frames (IEEE802 optional feature)<br>Removed Texas Instruments DP83848 and DP83849 temporarily for further                                                                                                                                                                                                                                                                                                                                                          |

| examination<br>Updated/clarified PHY requirements, PHY link loss reaction time is mandatory                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Added Texas Instruments DP83848, DP83849 with comments<br>Added PHYs which require Enhanced Link detection to be activated<br>Editorial changes                                                                                                                                                                                                                                                                                                                                                                                                           |

| PHY startup should not rely on MDC clocking<br>Added Microchip KSZ8041NL/TL Rev. A4 to list of example Ethernet PHYs for<br>EtherCAT with Enhanced Link Detection requirement<br>ESD tolerance and baseline wander compensation recommendations added<br>Editorial changes                                                                                                                                                                                                                                                                                |

| Completely revised and enhanced compatibility table<br>Editorial changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Added restrictions for ET1100-0002/ET1200-0002 and PHYs which require<br>Enhanced Link Detection: PHY address offset must be 0<br>PHY address offset for Teridian PHYs and Microchip KSZ8041 corrected                                                                                                                                                                                                                                                                                                                                                    |

| Added Microchip KSZ8051 PHYs<br>Link loss reaction time of Broadcom BCM5241is higher than data sheet reports<br>Clarified suitability of some Microchip/Texas Instruments PHYs for ET1100,<br>ET1200                                                                                                                                                                                                                                                                                                                                                      |

| Changed footnote: Microchip PIC10 is expected to be not suitable for management address conversion during an access (PIC10 remains suitable for adding an extra MDC cycle)                                                                                                                                                                                                                                                                                                                                                                                |

| Microchip KSZ8051: update to rev. A2<br>Microchip KSZ8721: LED1 speed behavior comments added<br>Texas Instruments DP83848/DP83849 comment on clock supply added<br>Renesas µPD60610, µPD60611, µPD60620, µPD60621 added<br>Microchip LAN8700 added<br>STMicroelectronics STE802RT1A/B PHYs added<br>Texas Instruments DP83620/ DP83630 added<br>Added chapter about EtherCAT over optical links<br>Added chapter about Gigabit Ethernet PHYs<br>Enhanced recommendations for Ethernet PHYs<br>Added recommendations to FX transceivers used for EtherCAT |

| Added Texas Instruments TLK105, TLK106, and TLK110<br>Added Microchip KSZ8081MNX,KSZ8081 MLX<br>Removed Microchip KSZ8721: not recommended for new designs by Microchip<br>(Microchip recommends KSZ8051 or KSZ8081 instead)<br>Renesas µPD60610, µPD60611, µPD60620, µPD60621 updated<br>Added IC Plus Corp. IP101G<br>IEEE802.3az Energy Efficient Ethernet must not be used<br>Added required PHX signals table                                                                                                                                        |

Updated to ET1100-0003/ET1200 -0003 Update to EtherCAT IP Core V3.0.2/V3.00c with FX support

| Version | Comment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.3     | <ul> <li>Renesas µPD60610/µPD60611: Auto-TX-Shift required (data sheet was updated)</li> <li>Renesas µPD60610/µPD60611/ µPD60620/µPD60621: MI link detection and configuration can only be enabled with certain IP Core versions</li> <li>Texas Instruments TLK105/TLK106/TLK110: MI link detection and configuration must not be enabled</li> <li>Microchip PHYs: added notes for an internal pull-up resistor at MDC pin</li> <li>Added note for PHYs with Enhanced link detection recommendation</li> <li>Editorial changes</li> </ul> |

| 2.4     | <ul> <li>Microchip PHYs: added comments regarding SPEED LED usage</li> <li>Added Microchip KSZ8061</li> <li>Added Texas Instruments TLK111</li> <li>PHY address offset recommendations for IP core relaxed because IP core supports any PHY address offset now.</li> </ul>                                                                                                                                                                                                                                                                |

| 2.5     | <ul> <li>Added note regarding odd nibble detection for Texas Instruments TLK105, TLK106, TLK110, TLK111</li> <li>Updated requirements for Texas Instruments DP83xxx PHYs, especially DP83849 restrictions with ET1100/ET1200</li> <li>Added Texas Instruments DP83822</li> <li>Changed recommended PHY address offset for Texas Instruments DP83620/DP83630/DP83640/DP83848: use offset 16 with ET1100-0003/ET1200-0003</li> </ul>                                                                                                        |

| 2.6     | <ul> <li>Changed recommended PHY address offset for Microchip KSZ8001L: use offset 16 with ET1100-0003/ET1200-0003</li> <li>Added Davicom Semiconductor DM9162 and DM9163</li> <li>Added Microchip KSZ8091MLX</li> <li>Added Microsemi VSC8530 and VSC8540</li> <li>Updated comments for Texas Instruments PHYs</li> <li>Editorial changes</li> </ul>                                                                                                                                                                                     |

| 2.7     | <ul> <li>Removed Marvell 88E3016 from incompatible PHY list, because IP Core supports RGMII</li> <li>Added Analog Devices ADIN1200</li> <li>Added EtherCAT G chapter and devices Analog Devices ADIN1300, Broadcom B50212E, Marvell 88E1111</li> </ul>                                                                                                                                                                                                                                                                                    |

Editorial changes

| Version | Comment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.0     | <ul> <li>Add reference to EtherCAT P</li> <li>Remove ESC10/ESC20</li> <li>Clarify EtherCAT PHY requirements, a</li> <li>Broadcom B50212E: Disable EEE by p</li> <li>Broadcom BCM54210, BCM54210S, BCM54210PE, BCM54210F, BCM54210S, BCM54210</li> <li>BCM54210, BCM54210S, BCM54210S</li> <li>BCM54214E, BCM54216E, BCM5422</li> <li>IC Plus IP101GA: Disable EEE by µC/device</li> <li>IC Plus IP1001C added</li> <li>Marvell 88E1111, 88E1510, 88E1510F 88E1518 added</li> <li>MaxLinear MxL86110, MxL86111 adde</li> <li>Microchip VSC8530, VSC8540: update sheet</li> <li>Microchip LAN8720A, LAN8740A, LANKSZ9131RNX, LAN8820, LAN8830, L</li> <li>Realtek RTL8201FR/FRI, RTL8201FI, Texas Instruments PHYs: update common Texas Instruments DP83825, DP83867IS</li> <li>Editorial changes</li> </ul> |

, add maintaining additional nibble y μC/Management Interface , BCM54210SE, BCM54210E, 4216E, BCM54220, BCM54220S, 0SE, BCM54210E, BCM54210PE, 220, BCM54220S added C/Management Interface; update to GA

0P, 88E1510Q, 88E1512, 88E1512P,

added date comments according to latest data

AN8741A, LAN88730, KSZ9031RNX, LAN8831, LAN8840, LAN8841 added FI, RTL8211F, RTL8211FS added mments

826, DP83867CR, DP83867IRRGZ, IS, DP83867E, DP83869HM added

### CONTENTS

| 1 | Overview   |                                                                      | 1  |

|---|------------|----------------------------------------------------------------------|----|

|   | 1.1        | EtherCAT P                                                           | 1  |

| 2 | EtherCAT ( | (100Mbit/s)                                                          | 2  |

|   | 2.1        | Requirements                                                         | 2  |

|   |            | 2.1.1 General requirements                                           | 2  |

|   |            | 2.1.2 Additional requirements using Beckhoff ESCs                    | 2  |

|   |            | 2.1.3 Additional requirements using Beckhoff ESCs with MII Interface | 2  |

|   | 2.2        | Recommendations                                                      | 3  |

|   |            | 2.2.1 General recommendations                                        | 3  |

|   |            | 2.2.2 Recommendations for 100BaseTX                                  | 3  |

|   |            | 2.2.3 Recommendations for 100BaseFX                                  | 3  |

|   | 2.3        | Example PHYs                                                         | 3  |

|   |            | 2.3.1 Example PHYs compatible with EtherCAT                          | 4  |

|   |            | 2.3.2 Example PHYs incompatible with EtherCAT                        | 8  |

|   | 2.4        | PHY connection                                                       | 8  |

|   |            | 2.4.1.1 Required Ethernet PHY signals                                | 9  |

|   | 2.5        | Clock supply                                                         | 9  |

|   | 2.6        | Gigabit Ethernet PHYs used for EtherCAT (100Mbit/s)                  | 9  |

|   | 2.7        | EtherCAT over optical links (100Base-FX)                             | 9  |

|   |            | 2.7.1 ESCs with native FX support                                    | 9  |

|   |            | 2.7.2 ESCs without native FX support                                 | 9  |

|   |            | 2.7.2.1 Standard Link Detection                                      | 9  |

|   |            | 2.7.2.2 Enhanced FX link detection                                   | 10 |

| 3 | EtherCAT ( | G (1000 Mbit/s)                                                      | 12 |

|   | 3.1        | Requirements                                                         | 12 |

|   |            | 3.1.1 General requirements                                           | 12 |

|   |            | 3.1.2 Additional requirements using Beckhoff ESCs                    | 12 |

|   | 3.2        | Recommendations                                                      | 12 |

|   | 3.3        | Example PHYs                                                         | 13 |

|   |            | 3.3.1 Example PHYs compatible with EtherCAT G                        | 14 |

|   | 3.4        | PHY Connection                                                       | 1  |

|   |            | 3.4.1 Required Ethernet PHY signals                                  | 1  |

|   | 3.5        | Clock supply                                                         | 1  |

| 4 | Appendix   |                                                                      | 2  |

|   | 4.1        | Support and service                                                  | 2  |

|   |            | 4.1.1 Beckhoff's branch offices and representatives                  | 2  |

|   | 4.2        | Beckhoff headquarters                                                | 2  |

|   |            |                                                                      |    |

#### 1 Overview

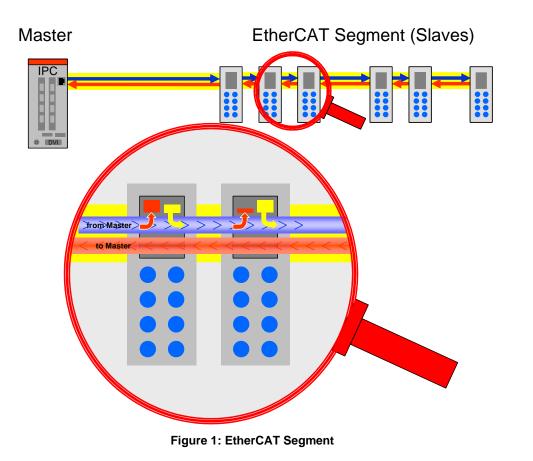

An EtherCAT Slave Controller (ESC) takes care of the EtherCAT communication as an interface between the EtherCAT fieldbus (Ethernet) and the slave application.

EtherCAT uses 100Mbit/s full duplex Ethernet communication. EtherCAT G uses 1,000Mbit/s full duplex Ethernet communication, and it also supports 100Mbit/s EtherCAT communication. EtherCAT Slave Controllers process Ethernet frames on the fly.

This application note provides an overview of the requirements to Ethernet PHYs used for EtherCAT and EtherCAT G devices. An example list of Ethernet PHYs currently expected to be suitable for EtherCAT/EtherCAT G is also provided.

This application note applies to the following Beckhoff EtherCAT Slave Controllers:

- ET1200-0003 •

- ET1100-0003 •

- EtherCAT IP Core for Altera®/AMD®(Xilinx®) FPGAs V3.0.2/V3.00c and later •

Refer to the ESC data sheets for further information. The ESC data sheets are available from the Beckhoff homepage (http://www.beckhoff.com).

#### EtherCAT P 1.1

For EtherCAT P, with integrated power supply, there are further requirements, described in the EtherCAT P Implementation Guide, available at the EtherCAT Technology Group homepage (http://www.ethercat.org).

### 2 EtherCAT (100Mbit/s)

This chapter is about Ethernet PHYs used for Beckhoff ESCs which support EtherCAT only (not EtherCAT G). For EtherCAT, the recommended interface is MII, since RMII/RGMII PHYs include TX FIFOs which increase the forwarding delay of an EtherCAT slave device, as well as the forwarding jitter.

EtherCAT and Beckhoff ESCs have some general requirements to Ethernet PHYs, which are typically fulfilled by state-of-the-art Ethernet PHYs. Refer to Section III of the ESC documentation for ESC specific information and supported features.

#### Requirements 2.1

#### General requirements 2.1.1

The PHYs have to comply with IEEE 802.3 100BaseTX or 100BaseFX, including:

- The PHYs have to support 100 Mbit/s Full Duplex links.

- The PHYs have to provide an MII (or RMII/RGMII<sup>1</sup>) interface.

- The PHYs have to use autonegotiation in 100BaseTX mode.

- The PHYs have to support the MII management interface.

- The PHYs have to support MDI/MDI-X auto-crossover in 100BaseTX mode.

- The PHYs must not modify the preamble length.

- The PHYs must not use IEEE802.3az Energy Efficient Ethernet.

- Minimum cable length is 0 m

- The PHYs must offer the RX ER signal (MII/RMII), or RX ER as part of the RX CTL signal (RGMII). RX ER must indicate invalid symbols both during frames and during inter-frame gap.

- The PHYs must maintain an **additional nibble** at the end of a frame (odd nibble, dribble nibble), without marking it with an RX ER.

- The PHYs have to provide a signal indicating a 100 Mbit/s (Full Duplex) link<sup>2</sup>, typically a configurable LED output. The signal polarity is active low or configurable for some ESCs. For RGMII, in-band status is sufficient, which should be enabled by default.

#### 2.1.2 Additional requirements using Beckhoff ESCs

#### PHY address

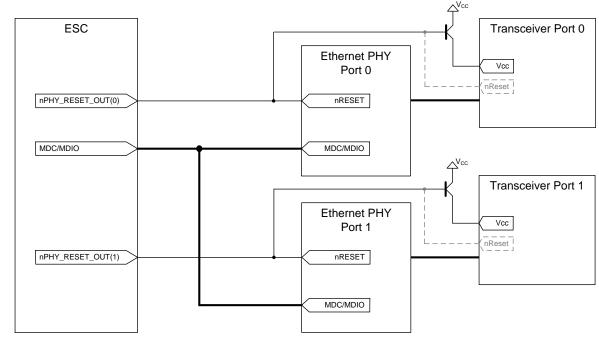

The Beckhoff ESCs use a shared MII Management Interface, so up to 4 different PHY addresses are required. The PHY addresses 0-3 are recommended, no address should be used as broadcast/isolate address.

When the PHY does not support addresses 0-3, the specific ESC features must be checked:

- Most ESCs require consecutive PHY addresses, except for the EtherCAT IP Core, which requires up to 3 individual addresses.

- Some ESCs also support a fixed offset, e.g. offset 16 for PHY addresses 16-19, or offset 1 for PHY addresses 1-4. Recommendation is to use offset 16, if that is not possible, offset 1.

#### PHY configuration

There is not necessarily a uController available in an EtherCAT device, which can configure a PHY. Therefore, PHY configuration must not rely on configuration via the MII management interface, i.e., required features must be enabled after power-on<sup>3</sup>, e.g., by default or by **strapping options**.

Only the EtherCAT IP Core supports basic configuration via MII management interface, especially advertisement of 100 Mbit/s Full Duplex when using Gigabit PHYs (MI Link detection and configuration). Any further configuration requires a µController attached to the ESC.

### MDC

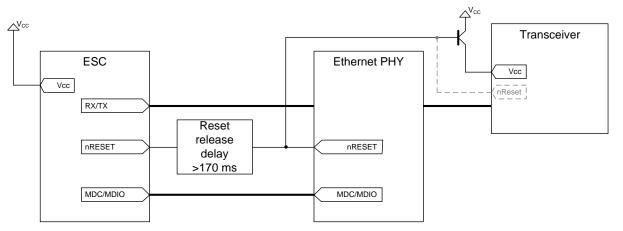

MII Management interface should not require additional MDC cycles, nor continuous MDC. PHY startup should not rely on MII management interaction, i.e., MDC clocking, since many ESCs do not communicate with the PHY via management interface unless the EtherCAT master requests this.

#### 2.1.3 Additional requirements using Beckhoff ESCs with MII Interface

The MII interfaces of Beckhoff ESCs are optimized for low processing/forwarding delays by omitting a transmit FIFO. To allow this, the Beckhoff ESCs have additional requirements to Ethernet PHYs, which are easily accomplished by several PHY vendors

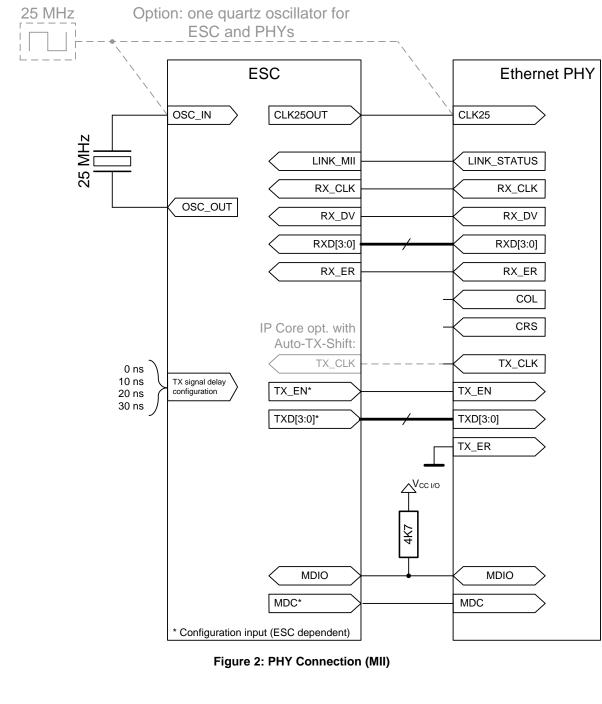

All PHYs connected to one ESC and the ESC itself must share the **same clock source**, so a TX FIFO can be omitted. This can be achieved by sourcing the PHYs from an ESC clock output or by sourcing the PHYs and the ESC from the same quartz oscillator. The phase offset between TX\_CLK and the clock input of the PHYs is compensated inside the ESC, either manually by configuration or automatically. The clock period cannot change between the PHYs and the ESC, since they have to share the same clock source.

There are two options for adjusting the phase relation of TX EN/TXD (generated by ESC) in relation to TX CLK (generated by the PHY):

Manual TX Shift compensation:

A static signal delay for TX EN/TXD by 0/10/20/30 ns is configured, which is used for all MII ports. Thus, all PHYs connected to one ESC must have the same fixed phase relation between TX CLK and the clock input of the PHY. The phase relation must be the same each time the PHYs are powered up/establish a link. The TX CLK signal is not connected to the ESC.

Automatic TX Shift compensation (IP Core only): The ESC detects the required phase shift automatically, based on the TX CLK signal. This is not the same function as a TX FIFO, the clock source still must be the same. But the PHYs are not required to have the same fixed phase relation each time they are powered on/establish a link.

<sup>&</sup>lt;sup>1</sup> RMII/RGMII is only supported by the EtherCAT IP Core

<sup>&</sup>lt;sup>2</sup> If a combined signal (100 MBit/s link with Full Duplex) is not available, a signal indicating a 100 Mbit/s link might be used. Take care that the link signal is inactive in case of no link. If only a Link signal is available, this might be used. Never use (combined) activity signals. Some PHYs toggle the 100 Mbit/s speed signal during autonegotiation, this is a problem for hotconnecting. Use a link signal in this case.

<sup>&</sup>lt;sup>3</sup> This is especially true for: link LED enable. EEE disable, preamble/additional nibble maintenance, RGMII in-band status enable.

#### 2.2 Recommendations

#### 2.2.1 General recommendations

- Receive and transmit delays should be deterministic, and as low as possible. They should comply with the standard (RX delay should be below ~320 ns, TX delay below ~140 ns).

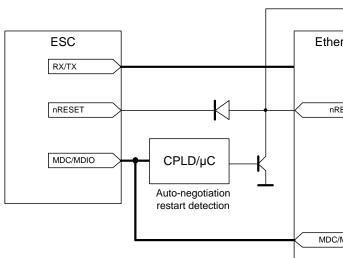

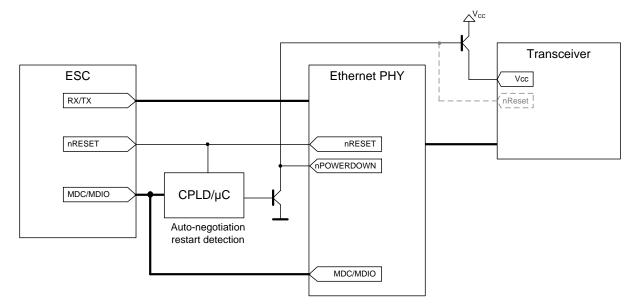

- PHY link loss reaction time (link loss to link signal/LED output change) should be faster than 15 µs to enable redundancy operation. Otherwise, Enhanced link detection in the ESC must be enabled. Enhanced link detection uses the RX\_ER signal, and it requires that the PHY asserts RX\_ER both inside and outside of frames for each invalid symbol. Enhanced link detection requires proper PHY address configuration.

- The PHYs should detect link loss within the link loss reaction time of 15 µs also if only one of the RX+ and RX- lines gets disconnected.

- ESD tolerance should be as high as possible (4kV or better)

- MDC should not incorporate pull-up/pull-down resistors, as this signal is used as a configuration input signal by some ESCs.

- PHY addresses should identify individual PHYs, using address 0-3. A broadcast address, or default isolate address can cause issues with supported PHY addresses.

- Power consumption should be as low as possible.

- I/O voltage: 3.3V should be supported for current ASIC and FPGA ESCs, additional 2.5V/1.8V I/O support is

recommended for recent FPGA ESCs.

- Single power supply according to I/O voltage.

- The PHY should use a 25 MHz clock source (quartz oscillator or ESC output).

- Industrial temperature range should be supported.

#### 2.2.2 Recommendations for 100BaseTX

- Maximum cable length should be ≥ 120 m to maintain a safety margin if the standard maximum cable length of 100 m is used.

- Baseline wander should be compensated (the PHYs should cope with the ANSI X3.263 DDJ test pattern for baseline wander measurements at maximum cable length, without frame loss).

- Restriction of Autonegotiation advertisement to 100 Mbit/s / Full Duplex is desirable (configured by hardware strapping options).

#### 2.2.3 Recommendations for 100BaseFX

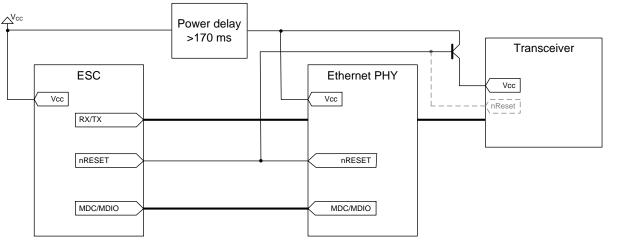

- Ethernet PHYs for 100BaseFX should implement Far-End-Fault (FEF) completely (generation and detection).

- The transceiver should have an input for disabling the transceiver/transmitter (for Enhanced FX link detection; e.g. enable, power-down or reset).

### 2.3 Example PHYs

In this chapter, some example Ethernet PHYs which are assumed to fulfill the EtherCAT requirements are presented, as well as an overview of Ethernet PHYs which are assumed to not fulfill these requirements. These lists represent a current collection of information from data sheets, vendors, and basic hardware tests for some devices, and they represent the best of **current knowledge**. These lists do not imply any kind of certification for EtherCAT, since none of these PHYs has been tested thoroughly to fulfill each individual EtherCAT or IEEE802.3 requirement. These lists are only intended for sharing current information about Ethernet PHYs for EtherCAT, and they are still **work-in-progress**.

The Ethernet PHYs were either judged by a **brief** overview of their data sheets or by additional **basic** hardware communication tests (basic hardware communication tests are indicated in the table).

The example Ethernet PHYs for EtherCAT shown in the following tables are sorted alphabetically by vendor name, not by preference. The selection of Ethernet PHYs was restricted to 1-4 port 10/100 Mbit/s Ethernet PHYs. These tables are incomplete in terms of Ethernet PHY vendors and Ethernet PHY devices – they just give some examples, and it is likely that other devices and devices from many vendors meet the requirements as well.

It cannot be guaranteed that the mentioned Ethernet PHYs, future revisions of them, or product changes are or will be fully EtherCAT compatible or not, nor that they are compatible with individual ESCs – because of ESC specific options (e.g., configurable link polarity, supported PHY address offsets, Enhanced Link detection, automatic TX Shift compensation). As far as known, restrictions and features of the PHYs impacting their EtherCAT usage are added to the tables.

Table 1 indicates for which ESC the PHY is assumed to be suitable, and which features have to be enabled and which settings have to be made for the ESC/PHY combination.

The main criteria are:

#### TX\_CLK fixed phase, Auto TX Shift

Some Ethernet PHYs cannot guarantee a fixed phase relation between their clock input and TX\_CLK. The Auto TX Shift feature compensates these phase shift variations. Auto TX Shift is not equivalent to a TX FIFO, it is just a controlled output phase for the TX signals. ESC and PHY have to share the same clock source anyway.

PHYs without a fixed phase for TX\_CLK require Auto TX Shift to be activated.

#### PHY address, PHY address offset

All ESCs support PHY addresses 0-3 for ports 0-3. ET1200/ET1100 also support an offset of 16, using PHY address 16-19. Future ESCs can support an offset of 1, using PHY address 1-4. The IP core since version 3.0.0 supports independent PHY addresses (including non-consecutive addresses).

#### Link signal

A link signal is required for MII/RMII. The ET1200 requires an active low signal, while ET1100 and IP core are configurable. For RGMII, In-band status is required.

#### Link loss reaction time, Enhanced Link Detection

Some Ethernet PHYs require **Enhanced Link Detection** to be activated in order to achieve sufficient link loss reaction times. Enhanced Link Detection is generally recommended because additional faults are detected and link loss reaction time is improved. Additionally, using Enhanced Link Detection allows an application specific configuration (robust communication vs. redundancy operation).

For back-to-back connections, Enhanced Link Detection must not be activated.

#### **EEE (Energy Efficient Ethernet)**

EtherCAT cannot use EEE, thus advertisement and usage have to be disabled. It must be disabled by default, by strapping, or using an additional  $\mu$ Controller, which disables this feature in the PHY using the PHY management interface.

### 2.3.1 Example PHYs compatible with EtherCAT

| Vendor / Device    | #<br>Ports | ET1200<br>suitable | ET1100<br>suitable | IP Core<br>suitable | Basic<br>HW<br>test⁴ | TX_CLK fixed phase <sup>5</sup>   | Auto-TX-Shift<br>(IP Core only) | PHY<br>addr. <sup>6</sup> | PHY<br>addr.<br>offset <sup>7</sup> | Link<br>loss<br>reaction<br>time | Enhanced Link<br>Detection | Comments                                                                                                                                       |

|--------------------|------------|--------------------|--------------------|---------------------|----------------------|-----------------------------------|---------------------------------|---------------------------|-------------------------------------|----------------------------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Analog Devices     |            |                    |                    |                     |                      |                                   |                                 |                           |                                     |                                  |                            |                                                                                                                                                |

| 78Q2123<br>78Q2133 | 1          |                    |                    | Х                   |                      |                                   | provisionally                   | 0/1                       | 0                                   |                                  | provisionally              | PHY addr. 0 = Broadcast. Only for single port devices, b                                                                                       |

| ADIN1200           | 1          | -                  | Х                  | Х                   | yes                  | yes (Data sheet)                  |                                 | 0-15                      | 0                                   | 0.6 µs                           | recommended9               |                                                                                                                                                |

| Broadcom           |            |                    |                    |                     |                      |                                   |                                 |                           |                                     |                                  |                            |                                                                                                                                                |

| BCM5221            | 1          | Х                  | Х                  | Х                   |                      | yes<br>(Data sheet <sup>8</sup> ) |                                 | 0-31                      | 0                                   | 1.3 µs                           | recommended9               | Requires additional write clock on MDC (supported by E v2.3.1/2.03b). Quartz oscillator required. Internal pull-do                             |

| BCM5222            | 2          | Х                  | Х                  | Х                   |                      | yes (Data sheet)                  |                                 | 0-31                      | 0                                   | 1.3 µs                           | recommended <sup>9</sup>   | Requires additional write clock on MDC (supported by E v2.3.1/2.03b). Quartz oscillator required. Internal pull-do                             |

| BCM5241            | 1          | Х                  | Х                  | Х                   | yes                  | yes (Data sheet)                  |                                 | 0-7, 8,<br>16, 24         | 0                                   | 45 µs                            | required                   | Requires additional write clock on MDC (supported by E v2.3.1/2.03b). Quartz oscillator required. Internal pull-up                             |

| Davicom Semicon    | ductor     |                    |                    |                     |                      |                                   |                                 |                           |                                     |                                  |                            |                                                                                                                                                |

| DM9161B            | 1          |                    |                    | Х                   |                      |                                   | provisionally                   | 0-31                      | 0                                   |                                  | provisionally              |                                                                                                                                                |

| DM9162             | 1          | -                  | -                  | Х                   |                      | no                                | required                        | 0-31                      | 0                                   | 1.79ms                           | required                   |                                                                                                                                                |

| DM9163             | 1          | -                  | -                  | Х                   |                      | no                                | required                        | 0-31                      | 0                                   | 1.79ms                           | required                   |                                                                                                                                                |

| IC Plus Corp.      |            |                    |                    |                     |                      |                                   |                                 |                           |                                     |                                  |                            |                                                                                                                                                |

| IP101ALF           | 1          |                    |                    | Х                   |                      |                                   | provisionally                   | 0-31                      | 0                                   |                                  | provisionally              | Link signal polarity depends on PHY address.                                                                                                   |

| IP101GA            | 1          |                    |                    | Х                   |                      |                                   | provisionally                   | 0-7                       | 0                                   |                                  | provisionally              | Link signal polarity depends on PHY address. Disable E                                                                                         |

| Marvell            |            |                    |                    |                     |                      |                                   |                                 |                           |                                     |                                  |                            |                                                                                                                                                |

| 88E3015<br>88E3018 | 1          | -                  | -                  | Х                   |                      | no                                | required                        | 0-31                      | 0                                   |                                  | provisionally              |                                                                                                                                                |

| LXT973             | 2          | (X)                | (X)                | Х                   | yes                  | probably                          | provisionally                   | 0-31                      | 0                                   | 1.9 ms                           | required                   | Measurements from the vendor with some LXT973 indic<br>a general statement could not be made. It is assumed th<br>ET1200/ET1100 are supported. |

#### Table 1: Example Ethernet PHYs assumed to fulfill EtherCAT requirements

because only one PHY address can be used. ET1100-0003, ET1200-0003, IP Core since down at MDC. ET1100-0003, ET1200-0003, IP Core since down at MDC. ET1100-0003, ET1200-0003, IP Core since up at MDC. XTALI voltage  $\leq$  1.8V. EEE by µC/Management Interface. licated that there is a fixed TX\_CLK phase relation, but that Auto-TX-Shift is not required and that

<sup>&</sup>lt;sup>4</sup> The following requirements were not part of the basic hardware test: MDI/MDI-X auto-crossover, MII management interface, TX clock phase relation, and preamble length maintenance. These requirements are assumed to be fulfilled either according to the data sheet or vendor notice. Hardware tests are typically performed with only one of the ESC types, e.g., IP Core.

<sup>&</sup>lt;sup>5</sup> Information about fixed phase shift between TX\_CLK and PHY clock source from data sheet or from vendor

<sup>&</sup>lt;sup>6</sup> PHY address range supported by PHY. Special PHY addresses are excluded (Broadcast/Isolate/Power down).

<sup>&</sup>lt;sup>7</sup> Suggested PHY address offset. ET1100 and ET1200 only support a PHY address offset of 0 or 16. A PHY address offset of 0 means PHY addresses 0-3 are used, an offset of 16 means PHY addresses 16-19 are used, etc..

<sup>&</sup>lt;sup>8</sup> Only for XTALI, not approved for REF\_CLK. According to Broadcom, a quartz oscillator can be connected to XTALI as well.

<sup>&</sup>lt;sup>9</sup> Recommended for IP Core only. Should not be enabled for ET1100/ET1200 (otherwise there is a potential risk of an additional link-down/link-up-cycle caused by ET1100/ET1200 directly after the link is re-established.

| Vendor / Device                      | #<br>Ports | ET1200<br>suitable | ET1100<br>suitable | IP Core<br>suitable | Basic<br>HW<br>test⁴ | TX_CLK fixed<br>phase⁵ | Auto-TX-Shift<br>(IP Core only) | PHY<br>addr. <sup>6</sup> | PHY<br>addr.<br>offset <sup>7</sup> | Link<br>loss<br>reaction<br>time | Enhanced Link<br>Detection | Comments                                                                                                                                                                                                                                                                                                                   |

|--------------------------------------|------------|--------------------|--------------------|---------------------|----------------------|------------------------|---------------------------------|---------------------------|-------------------------------------|----------------------------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Microchip                            |            |                    |                    |                     |                      |                        |                                 |                           |                                     |                                  |                            |                                                                                                                                                                                                                                                                                                                            |

| KSZ8001L<br>KSZ80010S                | 1          | х                  | х                  | х                   |                      | yes (Vendor)           |                                 | 1-31                      | 16                                  |                                  | provisionally              | PHY addr. 0 = Broadcast.<br>The KSZ8001 might have a pull-up resistor at the MDC p<br>resistor for strapping.<br>The SPEED LED might toggle during link up, causing los<br>Detection and Configuration or use LINK LED (requires e                                                                                         |

| KSZ8041TL<br>KSZ8041NL<br>KSZ8040FTL | 1          | -                  | -                  | х                   |                      | yes (Vendor)           |                                 | 1-7                       | 1                                   | 10 µs                            | recommended <sup>9</sup>   | Minimum Revision A4, which supports preamble mainten.<br>PHY addr. 0 = Broadcast. Enable 8 byte preamble with C<br>The SPEED LED might toggle during link up, causing lost<br>Detection and Configuration or use LINK LED (requires e<br>The KSZ8041 might have a pull-up resistor at the MDC p<br>resistor for strapping. |

| KSZ8051 MLL<br>KSZ8051 MNL           | 1          | X                  | х                  | Х                   |                      | yes (Vendor)           |                                 | 0-7                       | 0                                   | 5.3 µs                           | recommended <sup>9</sup>   | Minimum revision A2, which has a fixed TX_CLK phase.<br>Enable B_CAST_OFF to support PHY addr. 0 (otherwise<br>The KSZ8051 might have a pull-up resistor at the MDC p<br>resistor for strapping.<br>The SPEED LED might toggle during link up, causing lost<br>Detection and Configuration or use LINK LED (requires e     |

| KSZ8061MNX                           | 1          | -                  | -                  | Х                   |                      | yes (Data sheet)       |                                 | 1-7                       | 1                                   | 4.8 µs                           | recommended                | Disable Fixed RX PHY latency via management interface<br>PHY addr. 0 = Broadcast.                                                                                                                                                                                                                                          |

| KSZ8061MNG                           | 1          | X <sup>10</sup>    | X <sup>10</sup>    | Х                   |                      | yes (Data sheet)       |                                 | 0-7                       | 0                                   | 4.8 µs                           | recommended <sup>9</sup>   | Disable Fixed RX PHY latency via management interface<br>Enable B_CAST_OFF to support PHY addr. 0 (otherwise<br>The SPEED LED might toggle during link up, causing los<br>Detection and Configuration or use LINK LED (requires e                                                                                          |

| KSZ8061RNB<br>KSZ8061RND             | 1          | -                  | -                  | Х                   |                      | n. a.                  |                                 | 1-7                       | 1                                   | 4.8 µs                           | recommended                | RMII only.<br>Disable Fixed RX PHY latency via management interface<br>PHY addr. 0 = Broadcast.<br>The SPEED LED might toggle during link up, causing los<br>Detection and Configuration or use LINK LED (requires e                                                                                                       |

| KSZ8081MNX<br>KSZ8081MLX             | 1          | Х                  | х                  | Х                   |                      | yes (Data sheet)       |                                 | 0-7                       | 0                                   | 4.4 µs                           | recommended <sup>9</sup>   | Enable B_CAST_OFF to support PHY addr. 0 (otherwise<br>The KSZ8081 has a pull-up resistor at the MDC pin, whic<br>for strapping.<br>The SPEED LED might toggle during link up, causing los<br>Detection and Configuration or use LINK LED (requires e                                                                      |

| KSZ8091MLX                           | 1          | Х                  | х                  | Х                   |                      | yes (Data sheet)       |                                 | 0-7                       | 0                                   | 4.4 µs                           | recommended <sup>9</sup>   | Enable B_CAST_OFF to support PHY addr. 0 (otherwise<br>The KSZ8091 has a pull-up resistor at the MDC pin, whic<br>for strapping.<br>The SPEED LED might toggle during link up, causing lost<br>Detection and Configuration or use LINK LED (requires e                                                                     |

| LAN8187                              | 1          | -                  | -                  | Х                   |                      | no (Vendor)            | required                        | 0-31                      | 0                                   |                                  | provisionally              | Link signal polarity depends on PHY address.                                                                                                                                                                                                                                                                               |

| LAN8700                              | 1          | -                  | -                  | Х                   |                      | no (Vendor)            | required                        | 0-31                      | 0                                   |                                  | provisionally              | Link signal polarity depends on PHY address.                                                                                                                                                                                                                                                                               |

| LAN8710A                             | 1          | -                  | -                  | Х                   |                      | no                     | required                        | 0-7                       | 0                                   |                                  | provisionally              |                                                                                                                                                                                                                                                                                                                            |

| LAN8720A                             | 1          | -                  | -                  | Х                   |                      | n. a.                  |                                 | 0-1                       | 0                                   |                                  | provisionally              | RMII only.                                                                                                                                                                                                                                                                                                                 |

| LAN8740A                             | 1          | -                  | -                  | Х                   |                      |                        | provisionally                   | 0-7                       | 0                                   |                                  | provisionally              |                                                                                                                                                                                                                                                                                                                            |

| LAN8741A                             | 1          | -                  | -                  | Х                   |                      |                        | provisionally                   | 0-7                       | 0                                   |                                  | provisionally              |                                                                                                                                                                                                                                                                                                                            |

| LAN88730                             | 1          | -                  | -                  | Х                   |                      |                        | provisionally                   | 0-7                       | 0                                   |                                  | provisionally              |                                                                                                                                                                                                                                                                                                                            |

| VSC8530                              | 1          | -                  | -                  | Х                   |                      | no (Vendor)            | required                        | 0 or<br>0-31              | 0                                   | 10 µs                            | not necessary              | RMII/RGMII only.<br>LED configuration to Fast Link Fail by $\mu$ C/management in<br>Unmanaged mode: EEE disable by $\mu$ C/management inte<br>Managed mode: MAC interface configuration by $\mu$ C/mana                                                                                                                    |

| VSC8540                              | 1          | -                  | -                  | Х                   |                      | no (Vendor)            | required                        | 0-3 or<br>0-31            | 0                                   | 10 µs                            | not necessary              | LED configuration to Fast Link Fail by $\mu$ C/management in<br>Unmanaged mode: EEE disable by $\mu$ C/management inte<br>Managed mode: MAC interface configuration by $\mu$ C/mana                                                                                                                                        |

- pin, which might interfere with an external pull-down ost frames for a short period. Either enable MI Link enabling via management interface). enance. CONFIG[2:0]=100 (was PCS Loopback in Rev. A3). ost frames for a short period. Either enable MI Link enabling via management interface). pin, which might interfere with an external pull-down ise PHY addr. 0 = Broadcast). C pin, which might interfere with an external pull-down ost frames for a short period. Either enable MI Link s enabling via management interface). ace, otherwise preamble reduction possible. ace, otherwise preamble reduction possible. ise PHY addr. 0 = Broadcast). ost frames for a short period. Either enable MI Link s enabling via management interface). ace, otherwise preamble reduction possible. ost frames for a short period. Either enable MI Link s enabling via management interface). se PHY addr. 0 = Broadcast). hich might interfere with an external pull-down resistor ost frames for a short period. Either enable MI Link s enabling via management interface). ise PHY addr. 0 = Broadcast). hich might interfere with an external pull-down resistor

- ost frames for a short period. Either enable MI Link s enabling via management interface).

- t interface required. nterface required, only PHY address 0 anagement interface required

- t interface required.

- nterface required.

- anagement interface required

<sup>&</sup>lt;sup>10</sup> ET1100/ET1200 do not support/fully support MI management access from the µController, so external logic is required to access the PHY.

| Vendor / Device          | #<br>Ports | ET1200<br>suitable | ET1100<br>suitable | IP Core<br>suitable | Basic<br>HW<br>test⁴ | TX_CLK fixed phase <sup>5</sup> | Auto-TX-Shift<br>(IP Core only) | PHY<br>addr. <sup>6</sup> | PHY<br>addr.<br>offset <sup>7</sup> | Link<br>loss<br>reaction<br>time | Enhanced Link<br>Detection | Comments                                                                                                                                                                                                                                         |

|--------------------------|------------|--------------------|--------------------|---------------------|----------------------|---------------------------------|---------------------------------|---------------------------|-------------------------------------|----------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Realtek                  |            |                    |                    |                     |                      |                                 |                                 |                           |                                     |                                  |                            |                                                                                                                                                                                                                                                  |

| RTL8201N                 | 1          | -                  | -                  | Х                   |                      | no (Vendor)                     | required                        | 1-31                      | 16                                  |                                  | provisionally              | PHY addr. 0 = Power down.                                                                                                                                                                                                                        |

| RTL8201DL                | 1          | -                  | -                  | Х                   |                      | no (Vendor)                     | required                        | 0-7                       | 0                                   |                                  | provisionally              |                                                                                                                                                                                                                                                  |

| RTL8201FR<br>RTL8201FRI  | 1          | -                  | -                  | Х                   |                      | n. a.                           |                                 | 0-1                       | 0                                   |                                  | provisionally              | RMII only.<br>Configure link LED (LED1=LINK100) and disable EEE by                                                                                                                                                                               |

| RTL8201FI                | 1          | -                  | -                  | Х                   |                      |                                 | provisionally                   | 0-3                       | 0                                   |                                  | provisionally              | Configure link LED (LED1=LINK100) and disable EEE by                                                                                                                                                                                             |

| Renesas                  |            |                    |                    |                     |                      |                                 |                                 |                           |                                     |                                  |                            |                                                                                                                                                                                                                                                  |

| μΡD60610<br>μΡD60611     | 1          | -                  | -                  | Х                   |                      | no                              | required                        | 0/8/16/<br>24             | 0                                   | 3 x<br>RX_ER<br>(120 ns)         | not necessary              | MI Link detection and configuration can only be enabled for<br>V3.0.2/V3.00c<br>Link loss reaction time configurable via MII management in                                                                                                       |

| μΡD60620A<br>μΡD60621A   | 2          | Х                  | Х                  | Х                   |                      | yes (Data sheet)                |                                 | 0/8/16/<br>24+1           | 0                                   | 3 x<br>RX_ER<br>(120 ns)         | not necessary              | Set P1TXCL=0 for fixed TX_CLK phase shift.<br>EtherCAT support starts with order number UPD60620AG<br>MI Link detection and configuration can only be enabled for<br>V3.0.2/V3.00c<br>Link loss reaction time configurable via MII management in |

| STMicroelectronics       |            |                    |                    |                     |                      |                                 |                                 |                           |                                     |                                  |                            |                                                                                                                                                                                                                                                  |

| STE101P                  | 1          | -                  | -                  | Х                   |                      |                                 | provisionally                   | 1-31                      | 16                                  |                                  | provisionally              | PHY addr. 0 = Isolate.<br>MDC clock transition required to complete reset phase (MI<br>signal polarity depends on PHY address.                                                                                                                   |

| STE802RT1A<br>STE802RT1B | 1          | -                  | -                  | Х                   |                      | yes (Vendor)                    |                                 | 1-31                      | 16                                  |                                  | provisionally              | PHY addr. 0 = Isolate.<br>MDC clock transition required to complete reset phase (M                                                                                                                                                               |

by  $\mu$ C/Management Interface by  $\mu$ C/Management Interface

d for IP Cores starting with V2.4.3/V2.04d and

nt interface.

AGK-GAK-AX / UPD60621AGK-GAK-AX. d for IP Cores starting with V2.4.3/V2.04d and

nt interface.

(MI Link Detection and Configuration required). Link

(MI Link Detection and Configuration required).

| Vendor / Device               | #          | ET1200   | ET1100   | IP Core  | Basic       | TX_CLK fixed       | Auto-TX-Shift  | PHY    | PHY                          | Link                                                           | Enhanced Link                | Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------------------|------------|----------|----------|----------|-------------|--------------------|----------------|--------|------------------------------|----------------------------------------------------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Venuor / Device               | #<br>Ports | suitable | suitable | suitable | HW<br>test⁴ | phase <sup>5</sup> | (IP Core only) | addr.6 | addr.<br>offset <sup>7</sup> | loss<br>reaction<br>time                                       | Detection                    | Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Texas Instruments             |            |          |          |          |             |                    |                |        |                              |                                                                |                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DP83620<br>DP83630<br>DP83640 | 1          | Х        | Х        | Х        |             | yes (Vendor)       |                | 1-31   | 16                           | 250 μs<br>(conf. to<br>~1.3 μs)                                | required                     | PHY addr. 0 = Isolate. Do not use SCMII mode. Use LED add 2.2K $\Omega$ pull-down if necessary (e.g., ET1100/ET1200.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |